Reverse CPLD IC EPM7032AETI44-7 Eeprom JED File

Reverse CPLD IC EPM7032AETI44-7 Eeprom JED File

Reverse CPLD IC EPM7032AETI44-7 Eeprom JED File starts from unlocking the security fuse bit of cpld epm7032aeti44 chip, the embedded jed file will be extracted from cpld chip;

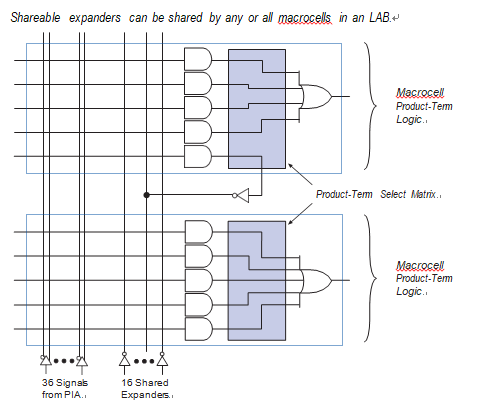

Each LAB has 16 shareable expanders that can be viewed as a pool of uncommitted single product terms (one from each macrocell) with inverted outputs that feed back into the logic array.

El archivo JED de reprom CPLD IC EPM7032AETI44-7 inverso comienza al desbloquear el bit de fusible de seguridad del chip CPLD EPM7032AETI44, el archivo JED incrustado se extraerá del chip CPLD;

Each shareable expander can be used and shared by any or all macrocells in the LAB to build complex logic functions when reading cpld dump information. A small delay (tSEXP) is incurred when shareable expanders are used. Figure 3 shows how shareable expanders can feed multiple macrocells.

Parallel expanders are unused product terms that can be allocated to a neighboring macrocell to implement fast, complex logic functions.

Parallel expanders allow up to 20 product terms to directly feed the macrocell OR logic, with five product terms provided by the macrocell and 15 parallel expanders provided by neighboring macrocells in the LAB.

The compiler can allocate up to three sets of up to five parallel expanders to the macrocells that require additional product terms when attacking cpld encrypted code. Each set of five parallel expanders incurs a small, incremental timing delay (tPEXP).

reverzní CPLD IC EPM7032AETI44-7 reprom JED soubor začíná odemknutím bezpečnostního pojistkového bitu čipu cpld epm7032aeti44, vložený soubor jed bude extrahován z čipu cpld;

For example, if a macrocell requires 14 product terms, the compiler uses the five dedicated product terms within the macrocell and allocates two sets of parallel expanders; the first set includes five product terms, and the second set includes four product terms, increasing the total delay by 2 ´ tPEXP.