Break PIC18F4220 Microcontroller Flash Memory

Break PIC18F4220 Microcontroller Flash Memory

Break PIC18F4220 microcontroller flash memory and eeprom memory fuse bit to restore embedded firmware of binary program or heximal data from secured PIC18F4220 microprocessor, original protective MICROCHIP MCU PIC18F4220 decryption is a destructive process;

Break PIC18F4220 microcontroller flash memory and eeprom memory fuse bit to restore embedded firmware of binary program or heximal data from secured PIC18F4220 microprocessor, original protective MICROCHIP MCU PIC18F4220 decryption is a destructive process;

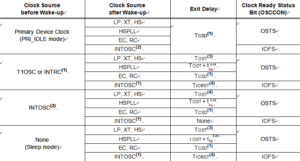

Normally, the device is held in Reset by the Oscillator Start-up Timer (OST) until the primary clock becomes ready from Break PIC18F4220 Microcontroller Flash Memory. At that time, the OSTS bit is set and the device begins executing code. If the internal oscillator block is the new clock source, the IOFS bit is set instead to Reverse Engineering ATMEL chip AT32UC3C264C flash.

briser le bit de fusible de la mémoire flash du microcontrôleur PIC18F4220 et de la mémoire EEPROM pour restaurer le micrologiciel intégré du programme binaire ou des données hexadécimales du microprocesseur PIC18F4220 sécurisé, le décryptage du microprocesseur MICROCHIP MCU PIC18F4220 de protection d’origine est un processus destructeur ;

The exit delay time from Reset to the start of code execution depends on both the clock sources before and after the wake-up and the type of oscillator if the new clock source is the primary clock from Reverse Engineering Chip ATMEGA644A code, Exit delays are summarized in below Table.

Code execution can begin before the primary clock becomes ready. If either the Two-Speed Start-up (see Section 23.3 “Two-Speed Start-up”) or Fail-Safe Clock Monitor (see Section 23.4 “Fail-Safe Clock Monitor”) is enabled, the device may begin execution as soon as the Reset source has cleared after Unlock Microcontroller Eeprom.

breek het flashgeheugen en eeprom-geheugen van de PIC18F4220-microcontroller om de ingebouwde firmware van een binair programma of heximale gegevens van een beveiligde PIC18F4220-microprocessor te herstellen, originele beschermende MICROCHIP MCU PIC18F4220-decodering is een destructief proces;

Execution is clocked by the INTOSC multiplexer driven by the inter- nal oscillator block. Execution is clocked by the internal oscillator block until either the primary clock becomes ready or a power-managed mode is entered before the primary clock becomes ready before Reverse Engineering Microcontroller ATmega644PA firmware; the primary clock is then shut down.

Certain exits from power-managed modes do not invoke the OST at all. There are two cases:

• PRI_IDLE mode, where the primary clock source is not stopped and

• the primary clock source is not any of the LP, XT, HS or HSPLL modes.

In these instances, the primary clock source is either already running (PRI_IDLE), or normally does not require an oscillator start-up delay (RC, EC and INTIO Oscillator modes) by Recover MCU ATmega162A Heximal. However, a fixed delay of interval TCSD following the wake event is still required when leaving Sleep and Idle modes to Break PIC18F4220 Microcontroller Flash Memory. Instruction execution resumes on the first clock cycle following this delay.