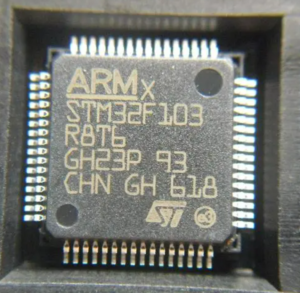

Attack Locked STM32F100R8 ARM MCU Flash Memory

Attack Locked STM32F100R8 ARM MCU Flash Memory

Attack Locked STM32F100R8 ARM MCU Flash Memory to extract microcontroller source code, and make microcontroller stm32f100r6 embedded firmware cloning;

STM32F100R8 power supply scheme will greatly improve the success rate of from its memory, hereby we will discuss and have better understanding about this process:

VDD = 2.0 to 3.6 V: External power supply for I/Os and the internal regulator. Provided externally through VDD

VSSA, VDDA = 0 to 3.6 V: External analog power supplies for ADC, Reset blocks, RCs and PLL (minimum voltage to be applied to VDDA is 2.4 V when the ADC is used). VDDA and VSSA must be connected to VDD and VSS, respectively.

هجوم مقفل STM32F100R8 ذاكرة فلاش ARM MCU لاستخراج شفرة مصدر متحكم ، وجعل متحكم stm32f100r6 جزءا لا يتجزأ من استنساخ البرامج الثابتة ؛

VBAT = 1.8 to 3.6 V: Power supply for RTC, external clock 32 kHz oscillator and backup registers (through power switch) when VDD is not present.

The device has an integrated power on reset (POR)/power down reset (PDR) circuitry. It is always active, and ensures proper operation starting from/down to 2 V. The device remains in reset mode when VDD is below a specified threshold, VPOR/PDR, without the need for an external reset circuit to facilitate the process of arm CPU stm32f100r8 flash memory breaking.

The device features an embedded programmable voltage detector (PVD) that monitors the VDD/VDDA power supply and compares it to the VPVD threshold. An interrupt can be generated when VDD/VDDA drops below the VPVD threshold and/or when VDD/VDDA is higher than the VPVD threshold. The interrupt service routine can then generate a warning message and/or put the MCU into a safe state. The PVD is enabled by software.

माइक्रोकंट्रोलर स्रोत कोड निकालने के लिए एआरएम एमसीयू फ्लैश मेमोरी STM32F100R8 हमला बंद, और माइक्रोकंट्रोलर STM32F100R8 एम्बेडेड फर्मवेयर क्लोनिंग बनाना;

The regulator has three operation modes: main (MR), low power (LPR) and power down.

- l MR is used in the nominal regulation mode (Run)

- l LPR is used in the Stop mode

- l Power down is used in Standby mode: the regulator output is in high impedance: the kernel circuitry is powered down, inducing zero consumption (but the contents of the registers and SRAM are lost)

This regulator is always enabled after reset to Break IC. It is disabled in Standby mode, providing high impedance output.