ARM Microcontroller STM32F051C4 Flash Binary Recovery

ARM Microcontroller STM32F051C4 Flash Binary Recovery

ARM Microcontroller STM32F051C4 Flash Binary Recovery means the embedded firmware of mcu stm32f051c4 will be copied from original chip stm32f051c4 which has been attacked by removing locked bit protection;

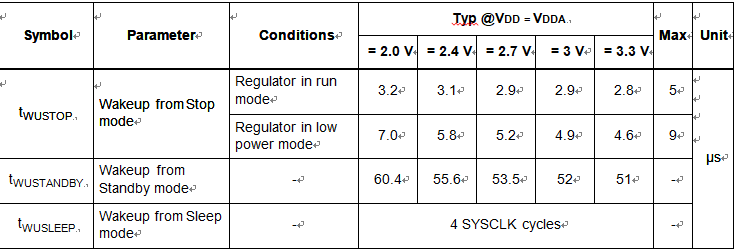

The wakeup times given in Table 32 are the latency between the event and the execution of the first user instruction. The device goes in low-power mode after the WFE (Wait For Event) instruction, in the case of a WFI (Wait For Interruption) instruction, 16 CPU cycles must be added to the following timings due to the interrupt latency in the Cortex M0 architecture.

The SYSCLK clock source setting is kept unchanged after wakeup from Sleep mode. During wakeup from Stop or Standby mode, SYSCLK takes the default setting: HSI 8 MHz in the process of recovering source code from ic mcu stm32f107rc.

ARM-Mikrocontroller STM32F051C4 Flash Binärwiederherstellung bedeutet, dass die eingebettete Firmware von mcu stm32f051c4 vom ursprünglichen Chip stm32f051c4 kopiert wird, der durch Entfernen des gesperrten Bitschutzes angegriffen wurde;

The wakeup source from Sleep and Stop mode is an EXTI line configured in event mode. The wakeup source from Standby mode is the WKUP1 pin (PA0).

All timings are derived from tests performed under the ambient temperature and supply voltage conditions summarized in Table 20: General operating conditions.