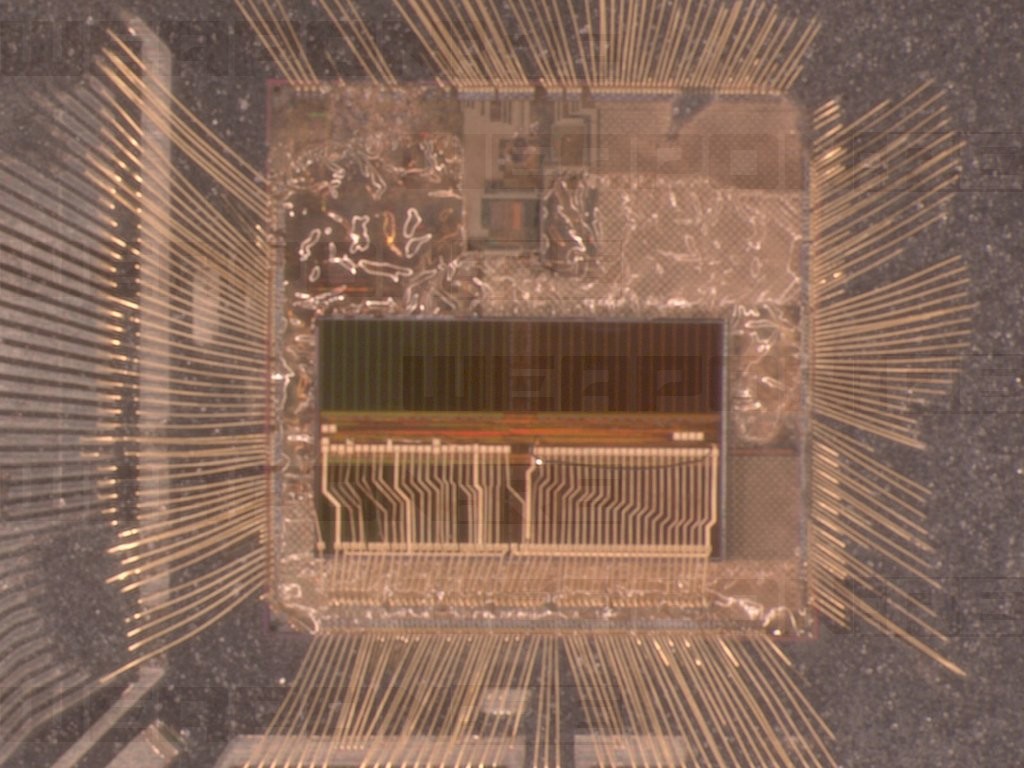

Altera CPLD EPM7256ATC144 Chip Eeprom Data Decoding

Altera CPLD EPM7256ATC144 Chip Eeprom Data Decoding

Altera CPLD EPM7256ATC144 Chip Eeprom Data Decoding needs to crack altera pld epm7256atc protective system and reset the status of CPLD IC from locked to unlock, extract embedded software from IC CPLD chip;

- See the Operating Requirements for Altera Devices Data Sheet.

- Minimum DC input voltage is –0.5 V. During transitions, the inputs may undershoot to –2.0 V for input currents less than 100 mA and periods shorter than 20 ns.

- For EPM7128A and EPM7256A devices only, VCC must rise monotonically.

- In MAX 7000AE devices, all pins, including dedicated inputs, I/O pins, and JTAG pins, may be driven before VCCINT and VCCIO are powered.

- These devices support in-system programming for –40° to 100° C. For in-system programming support between –40° and 0° C, contact Altera Applications.

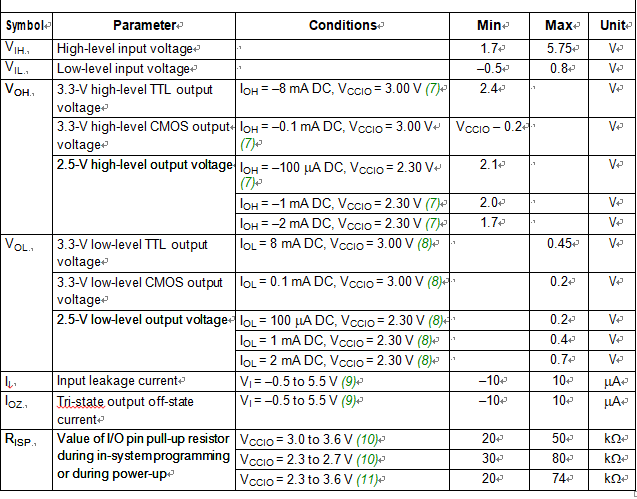

These values are specified under the recommended operating conditions shown in Table 14 on page 28.

Le décodage de données de la puce Altera CPLD EPM7256ATC144 doit déchiffrer le système de protection Altera PLD EPM7256ATC et réinitialiser l’état de CPLD IC de verrouillé à déverrouiller, extraire le logiciel embarqué de la puce IC CPLD;

The parameter is measured with 50% of the outputs each sourcing the specified current. The IOH parameter refers to high-level TTL or CMOS output current for the purpose of recovering altera cpld epm7128alc eeprom program.

The parameter is measured with 50% of the outputs each sinking the specified current. The IOL parameter refers to low-level TTL or CMOS output current.

This value is specified for normal device operation. For MAX 7000AE devices, the maximum leakage current during power-up is ±300 mA. For EPM7128A and EPM7256A devices, leakage current during power-up is not specified which is especially useful features for recover cpld epm7032vtc system memory content.

(10) For EPM7128A and EPM7256A devices, this pull-up exists while a device is programmed in-system.

For MAX 7000AE devices, this pull-up exists while devices are programmed in-system and in unprogrammed devices during power-up.

Capacitance is measured at 25 °C and is sample-tested only. The OE1 pin (high-voltage pin during programming) has a maximum capacitance of 20 pF.

The POR time for MAX 7000AE devices (except MAX 7128A and MAX 7256A devices) does not exceed 100 ms. The sufficient VCCINT voltage level for POR is 3.0 V. The device is fully initialized within the POR time after VCCINT reaches the sufficient POR voltage level.